Page Outline

- Page Outline

- ZYNQ 7000-Series FPGA: 32-Bit RISC-V CPU

- Logicism: 32-Bit RISC-V CPU

- C-Language-Version NumPy

- NMOS Device Design

- Gitlet

- FIFO-and-UART Piano

- Philphix

- Build Your Own World - Avatar-Controlled Maze Game

- 2048

- Deque

- Voice-Activated Robot Car

- Scheme Interpreter

- Cats

- Ants

- Hog

ZYNQ 7000-Series FPGA: 32-Bit RISC-V CPU

- Spring 2022, EECS151 Course Final Project

- Xilinx Vivado

- Verilog, System Verilog

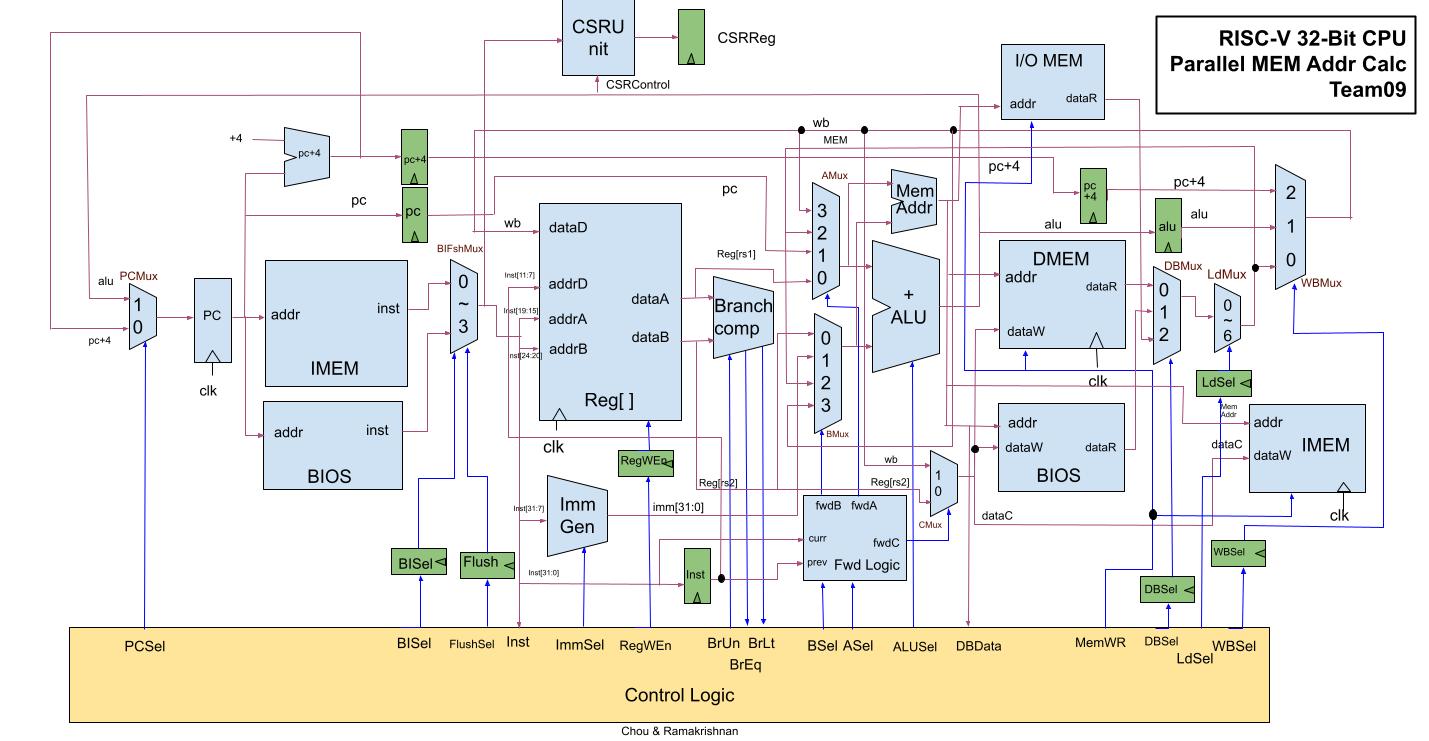

A project using Verilog where Viraj Ramakrishnan and I built a 32-bit three-stage pipelined RISC-V CPU with synchronous read-and-write memory. This CPU features with 40 supported assembly instructions, BIOS memory, and memory mapped I/O for UART. It also achieves CPI 1.18 and clocks at 66.7 MHz.

The CPU above is one of our designs which was implemented with paralleled memory.

Click Here to View the Final Project Report in Full Window

More project specification can be found at Spring 2022 EECS151LB FPGA Final Project’s Github.

Logicism: 32-Bit RISC-V CPU

- Fall 2021, CS61C Course Project

- Python, Logicism

A project using Logicism where I built a 32-bit two-stage pipelined RISC-V CPU with synchronous read-and-write memory. This CPU streamlines compiling process of RISC-V programs by 37 supported assembly instructions such as add, sw, lw, and jal etc.. This streamlined CPU achieved 99.5% coverage rate with 7 circ. type files.

More project specification can be found at Fall 2021 CS61C Project 3: CS61CPU.

C-Language-Version NumPy

- Fall 2021, CS61C Course Project

- Plain C

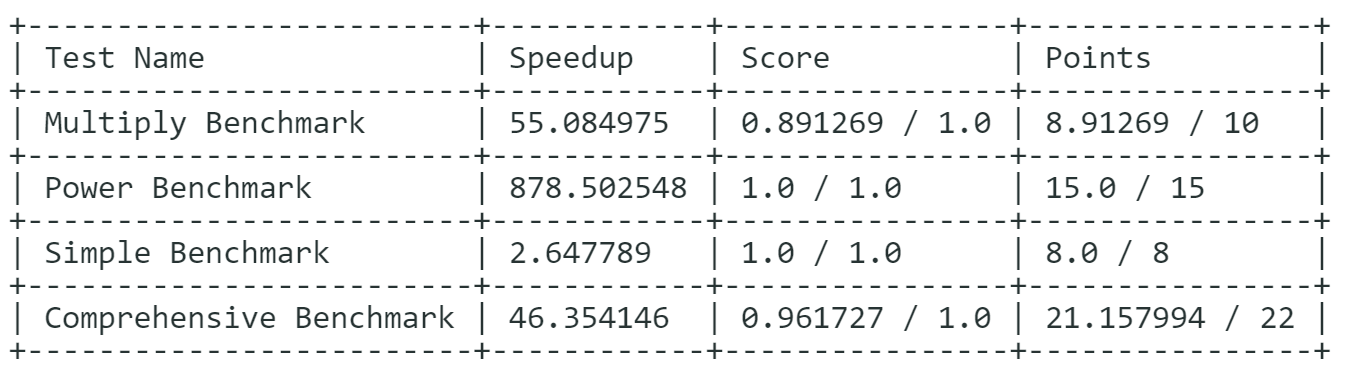

A project using C language to build NumPy, a powerful python library that supports for large, multi-dimensional array and matric computation. The purpose of this project is to understand the features of C language such as fast and efficient memory management, portability, and extensibility. This library featured with matrix operations such as add, multiplication, and power, whose algorithms were optimized by SIMD, OpenMP, paralleling, and loop unrolling. The final product achived 878.5 speed-up rate in power of a matrix and 55.1 speed-up rate in matrix multiplication on CS61C Benchmark.

More project specification can be found at Fall 2021 CS61C Project 4: Numc.

NMOS Device Design

- Fall 2021, EE130 Course Final Project

- TCAD

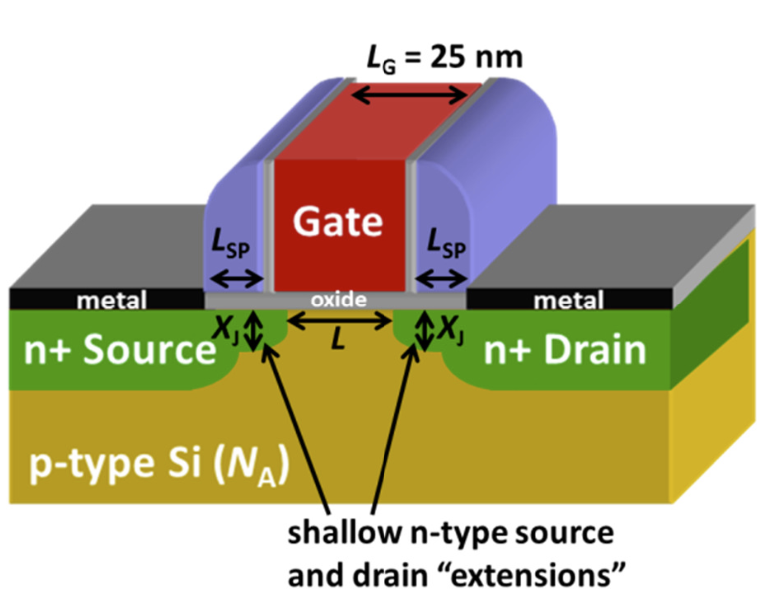

A project using TCAD (Sentauras) to simulate the behavior of customized NMOS. The goal for this project is to let students be familiar with how a transistor is designed where we have to account for specification and tradeoffs. The given requirements were that all customized NMOSs should meet I_on (saturated current) >= 400 uA per um channel width and I_off <= 1nA per um channel width with given costrants. Fan Xia and I’s design achieved I_on 0.00409 A and I_off 3.158 * 10^-10 A, denoting I_on/I_off to be 1296123.50.

Due to academic intergrity, the picture above is for demo only. For more details about our design, please reach me out :)

Gitlet

- Spring 2021, CS61B Course Project

- Data Structure

- Java

A project using Java to simulate GitHub, a version-control system, built from scratch to 1500+ lines of code. The goal of this project is to be familiar with data structure, espectially hashmap, and object-oriented program. This Gitlet supports 13 enssential git commands such as add, commit, status, branch, checkout, log, and merge. It is also implemented with one customized command find which can search and match the user-provided keywords with most relevent commit in all commited messages.

FIFO-and-UART Piano

- Spring 2022, EECS151LB Course Project

- Xilinx Vivado

- Verilog, System Verilog

Philphix

- Fall 2021, CS61C Course Project

- Data Structure

- Plain C

More project specification can be found at Fall 2021 CS61C Project 1: Philphix.

Build Your Own World - Avatar-Controlled Maze Game

- Spring 2021, CS61B Course Project

- Data Structure

- Java

More project specification can be found at Spring 2021 CS61B Project 3: Build Your Own World.

2048

- Spring 2021, CS61B Course Project

- Data Structure

- Java

More project specification can be found at Spring 2021 CS61B Project 0: 2048.

Deque

- Spring 2021, CS61B Course Project

- Data Structure

- Java

More project specification can be found at Spring 2021 CS61B Project 1: Data Structures.

Voice-Activated Robot Car

- Spring 2021, EECS16B Course Final Project

- Launchpad, Arduino, Python

Scheme Interpreter

- Fall 2020, CS61A Course Project

- Python

More project specification can be found at Fall 2020 CS61A Project 4: Scheme.

Cats

- Fall 2020, CS61A Course Project

- Python

More project specification can be found at Fall 2020 CS61A Project 2: Cats.

Ants

- Fall 2020, CS61A Course Project

- Python

More project specification can be found at Fall 2020 CS61A Project 3: Ants.

Hog

- Fall 2020, CS61A Course Project

- Python

More project specification can be found at Fall 2020 CS61A Project 1: Hog.